12月13日消息,据semiwiki报道,模拟单元的设计和迁移与数字单元完全不同,因为模拟单元的输入和输出通常随着时间的推移具有连续可变的电压电平,而不仅仅是在 1 和 0 之间切换。台积电的Kenny Hsieh在最近的北美OIP活动中就模拟设计迁移的主题进行了演讲。

模拟单元挑战

从台积电N7到N5再到N3,模拟设计规则的数量急剧增加,同时需要考虑更多的布局效应。模拟单元的高度往往是不规则的,所以没有像标准单元那样的基台(abutment)。附近的晶体管布局会影响相邻晶体管的性能,需要花费更多时间进行验证。

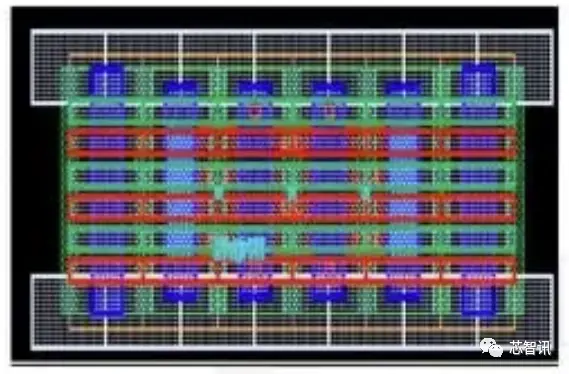

台积电从N5节点开始对模拟单元采取的方法是使用具有固定单元高度的布局,支持单元的基台以形成阵列,重复使用 Metal 0 及以下的预绘制布局,并且经过硅验证。模拟单元的 PDK 内部是有源单元,加上所有其他参数:CMOS、保护环、CMOS tap、变容二极管等。

模拟单元现在使用固定高度,放置在轨道(track)中,您可以在其中使用基台,甚至可以自定义过渡(transition)、tap和保护区域。模拟单元的所有可能组合都经过详尽的预验证。

模拟单元

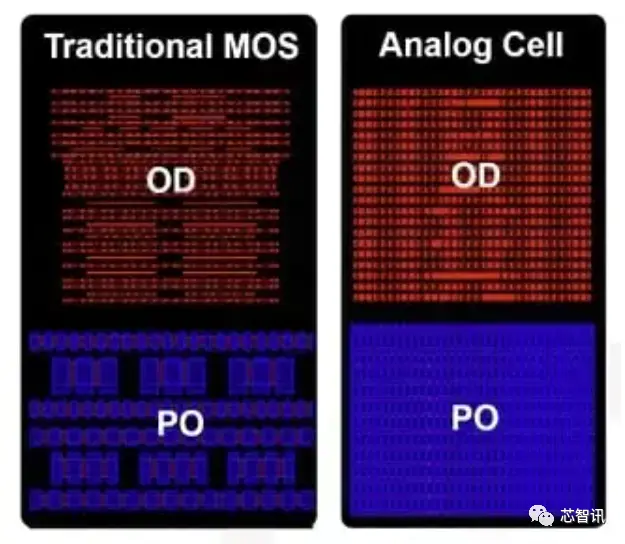

通过这种模拟单元方法,具有均匀的氧化物扩散(OD)和多晶硅(PO),从而提高了硅产量。

模拟单元布局

自动化模拟单元布局

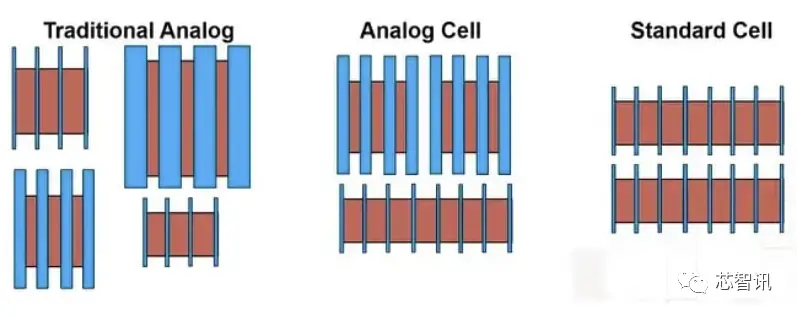

通过限制模拟单元内的模拟晶体管使用更有规律的模式,那么就可以更容易地使用布局自动化,如:使用模板自动布局、具有电气感知宽度和空间的自动布线,以及添加备用晶体管以支持设计过程中后来出现的任何ECO。

模拟单元的常规布局

在节点之间迁移时,原理图拓扑结构被重新使用,而每个器件的宽度和长度确实发生了变化。APR的设置是针对单元中的每个模拟元件进行调整的。对电流和寄生匹配等模拟指标的APR约束使这个过程更加智能。为了支持ECO流程,有一个自动备用晶体管插入的功能。自2021年以来,Cadence和Synopsys都与台积电合作,以实现这种改进的模拟自动化方法。

将模拟电路迁移到新的工艺节点需要一系列设备映射、电路优化、版图重用、模拟 APR、EM 和 IR 修复以及版图后仿真。在映射期间,使用 Id 饱和方法,其中器件根据其上下文自动识别。

伪布局后仿真可以使用估计值和一些完全提取的值来缩短分析循环。Cadence和Synopsys对IC布局工具的增强现在支持原理图迁移、电路优化和版图迁移步骤。

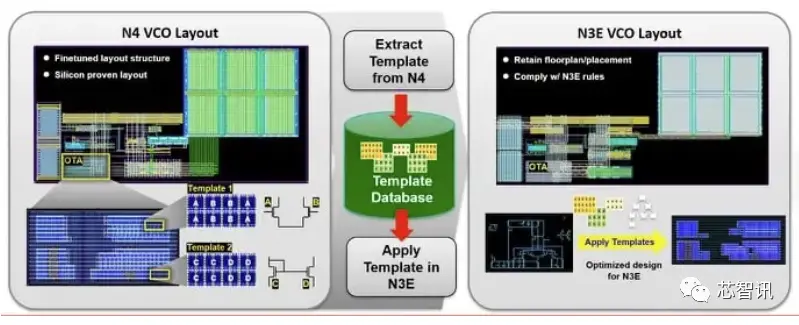

使用自动化步骤和模板方法将 N4 的 VCO 布局迁移到 N3E 节点,重用差分对和电流镜像设备的布局和方向。将新的自动化迁移方法与手动方法进行比较,其中手动迁移所需时间为 50 天,而自动化仅需 20 天,因此生产率提高了 2.5 倍。早期的 EM、IR 和寄生 RC 检查是实现生产力提升的基础。

N4 到 N3E VCO 布局迁移

基于环形的VCO也使用Pcell手动和自动从N40节点迁移到N22节点。通过使用自动化流程,生产率提高了 2 倍。Pcells有更多的限制,所以生产力的提高要少一些。

总结

台积电通过以下方式应对模拟小区迁移的挑战:与 Cadence 和 Synopsys 等 EDA 供应商合作修改其工具,使用具有固定高度的模拟小区以实现更多的布局自动化,并采用与数字流类似的策略。两个迁移示例表明,当使用较小的节点(如 N5 到 N3)时,生产力提高可以达到 2.5 倍。即使使用像 N40 这样的成熟节点,您也可以期望使用 Pcell 将生产率提高 2 倍。

编辑:芯智讯-林子