近日台积电董事长Mark Liu(刘德音)在IEEE上刊登了一篇长文,标题为《How We’ll Reach a 1 Trillion Transistor GPU》。

作为全球半导体产业巨头,Mark Liu讲述了AI产业发展背后的芯片故事,视角独特,非常值得一读。

(1)10年内将出现万亿晶体管集成的GPU

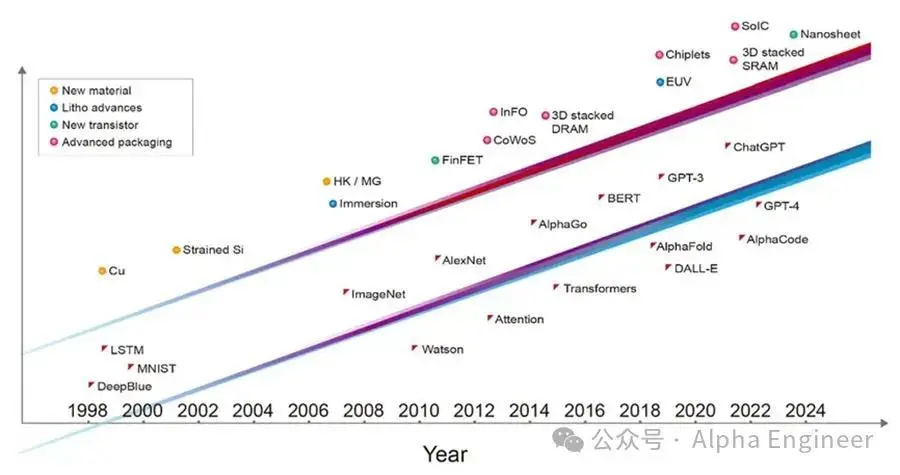

从1997年IBM Deep Blue击败国际象棋大师Garry Kasparov算起,到ChatGPT、Sora的诞生,过去了整整27年。

这27年中,人工智能的能力得到了极大的提升,这背后有三大驱动力:算法架构的创新、海量数据的积累、半导体技术的革命。

可以说,半导体产业的技术革新,是人工智能发展的重要驱动力。

IBM的Deep Blue采用的是0.6微米和0.35微米的混合芯片制造工艺。

赢得ImageNet竞赛的神经网络模型,背后是基于40纳米制程的芯片工艺。

在围棋界独霸天下的AlphaGo,采用的是28nm的制程工艺。

轰动全球的ChatGPT,则是基于4nm工艺。

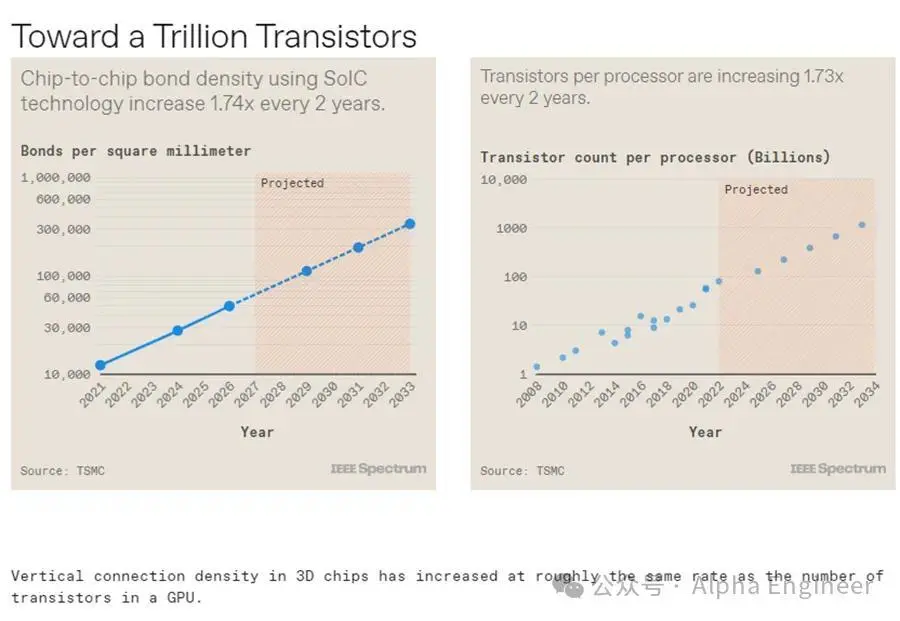

如果AI革命按现在的速度发展下去,10年内我们就需要一个万亿晶体管的GPU。

而要知道,英伟达最新发布的Blackwell架构的B200芯片,也才只有2080亿个晶体管。也就是说,10年内GPU中晶体管的集成数量将有10倍的提升空间。

半导体技术进步的驱动力包括:新材料、光刻技术发展、新型晶体管、先进封装工艺。上图中把这四种类型的驱动因素分别呈现,一目了然。

(2)光刻工艺达到瓶颈,3D封装成为突破口

自集成电路发明以来,半导体技术一直致力于缩小尺寸,从而能够将更多的晶体管塞进一个拇指大小的芯片中。

现如今,随着2.5D、3D封装被广泛应用,集成度提升到了新的水平。

台积电正在将许多芯片组合成为一个紧密集成的、大规模互联的系统。这是半导体集成领域正在发生的范式转变。

在AI时代,晶体管的集成度变得愈发重要。这是因为光刻机在加工芯片的过程中,有一个非常重要的物理限制,即不能制造超过800 mm²尺寸的集成电路。

更具体来说,这个数字是858 mm²(26 mm ×33 mm),可以理解为光刻机可处理的芯片极限尺寸,在业内被称为Reticle Limit。

因此,人们无法通过单纯做大芯片尺寸来提升性能。

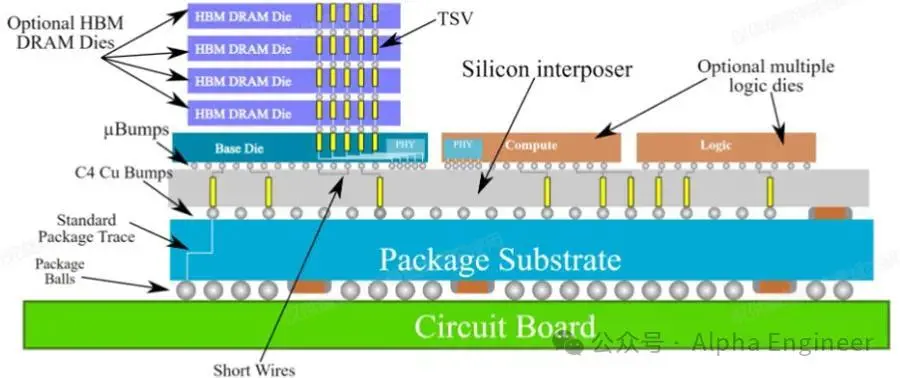

现如今,我们可以通过将多个芯片连接到一块更大的中介层上(interposer),从而突破光刻机Reticle Limit的性能瓶颈,在单一系统中集成更多的晶体管。

例如,台积电著名的CoWoS技术(Chip-on-Wafer-on-Substrate)可以容纳多达6个掩膜板区域的计算芯片,以及十几个HBM芯片。

(3)CoWoS先进封装在Nvidia GPU中的应用

台积电的CoWoS技术已经被广泛应用于Nvidia的GPU中,包括Ampere架构及Hopper架构的GPU。

它们均由一块GPU芯片和6个HBM共同集成在硅中介层上,计算芯片的尺寸大约是当前芯片制造工艺允许的最大尺寸。

Ampere架构的GPU采用7nm工艺,集成了540亿个晶体管。

Hopper架构的GPU采用4nm工艺,集成了800亿个晶体管。

制程工艺的提升使得我们能够在相同的表面积上多封装50%的晶体管数量,从而有效支持ChatGPT这类大语言模型的训练及推理。

图:Nvidia芯片架构演进历史,申万宏源

(4)HBM、Bumpless Bonding:高性能GPU的基石

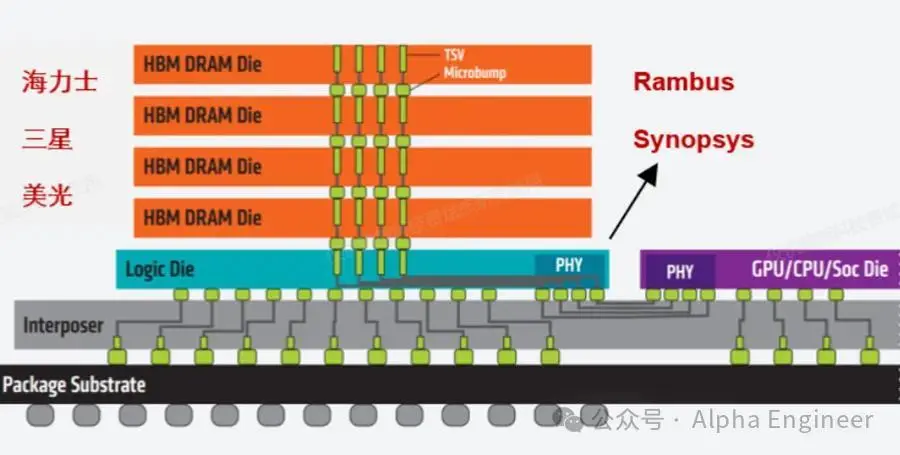

另一项关键的半导体技术是HBM。

HBM在控制逻辑IC之上,垂直堆叠了若干DRAM芯片,并采用TSV(硅通孔)进行垂直互联,让信号能够穿过每个芯片的焊锡凸点,从而形成存储芯片之间的连接。

这种将芯片堆叠在一起形成集成系统的能力,在台积电被称为SoIC(System-on-Integrated Chips)。

现如今,高性能GPU基本离不开HBM。

根据台积电的最新技术3D SoIC,可以将现在的HBM方案进行“无凸块化”处理(bumpless bonding)。

新版HBM架构采用铜对铜的连接,用混合键合技术堆叠12层芯片,并且在低温下粘合在一块较大的逻辑芯片之上,总厚度仅为600微米。

新版HBM架构能够提供更密集的垂直互联,铜对铜连接的密度显著高于焊锡凸块所提供的集成密度。

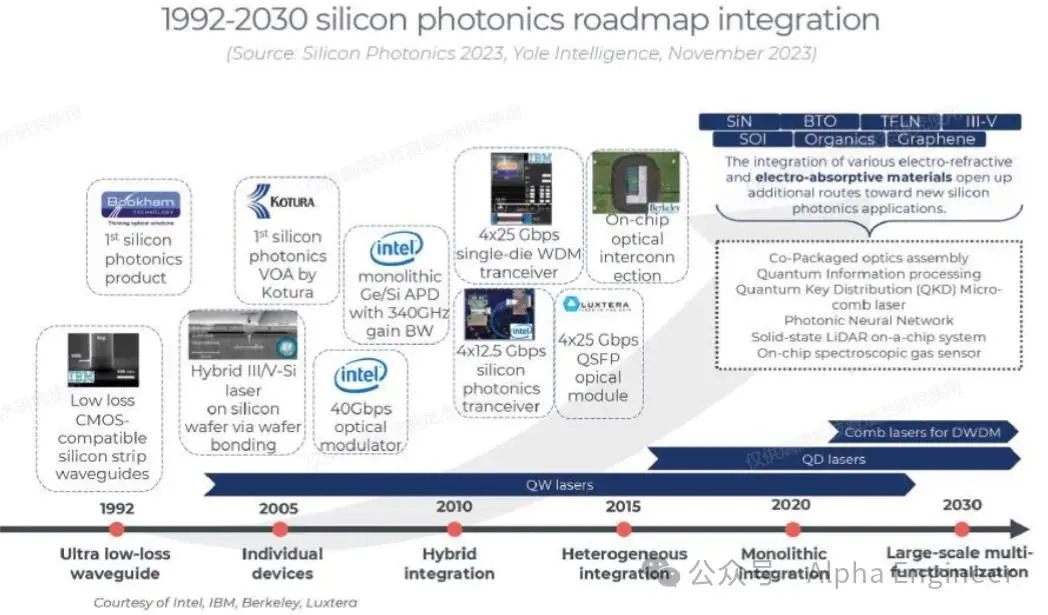

(5)硅光:未来半导体产业最重要的技术之一

对于大语言模型而言,有高性能芯片还不够。为了达到极高的计算速度,我们还需要提升通信速率。

现如今,光学互联已经被广泛应用于数据中心里的服务器机架。不久之后,我们就会需要通过基于硅光的光学接口,来将GPU和CPU封装在一起。

这样一来,数百台服务器可以对外表现为一个具备统一内存的巨型GPU。

随着AI应用需求的推动,硅光将成为未来半导体产业最重要的技术之一。

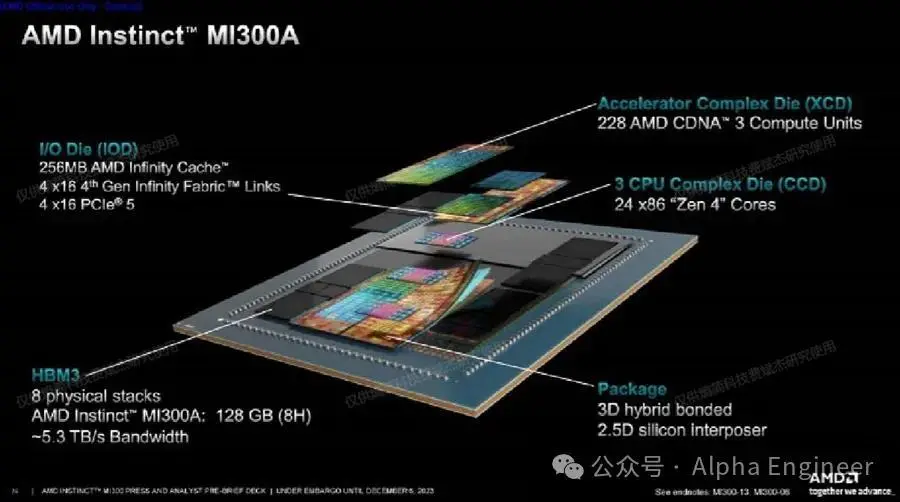

(6)CoWoS先进封装在AMD MI300A中的应用

AMD的MI300A加速处理单元不仅仅运用了CoWoS,还用到了台积电的SoIC技术。

MI300A同时包含了GPU和CPU核心,其中GPU负责处理AI任务所需的密集矩阵乘法运算,而CPU负责控制整个系统的运算,HBM则统一为二者提供服务。

9个基于5nm制程的计算芯片,堆叠在4个基于6nm制程的基础芯片上,后者主要负责缓存和IO通信。处理器的计算部分包含了1500亿个晶体管。

当下,单块GPU芯片已经达到了光刻工艺的制造极限(reticle limit),晶体管数量约1000亿个。为了继续增加晶体管集成度,势必需要将多个chiplet通过2.5D或3D封装的方式来集成互联,执行运算。

幸运的是,业界已经能够快速缩小chiplet之间垂直互联的间距,从而提升连接密度,并且还有非常充足的提升空间。

我们认为通过垂直互联技术的发展,晶体管的集成密度可以至少提成一个数量级,使得多芯片GPU内集成超过1万亿个晶体管。

(7)EEP仍将保持每2年翻3倍的增长趋势

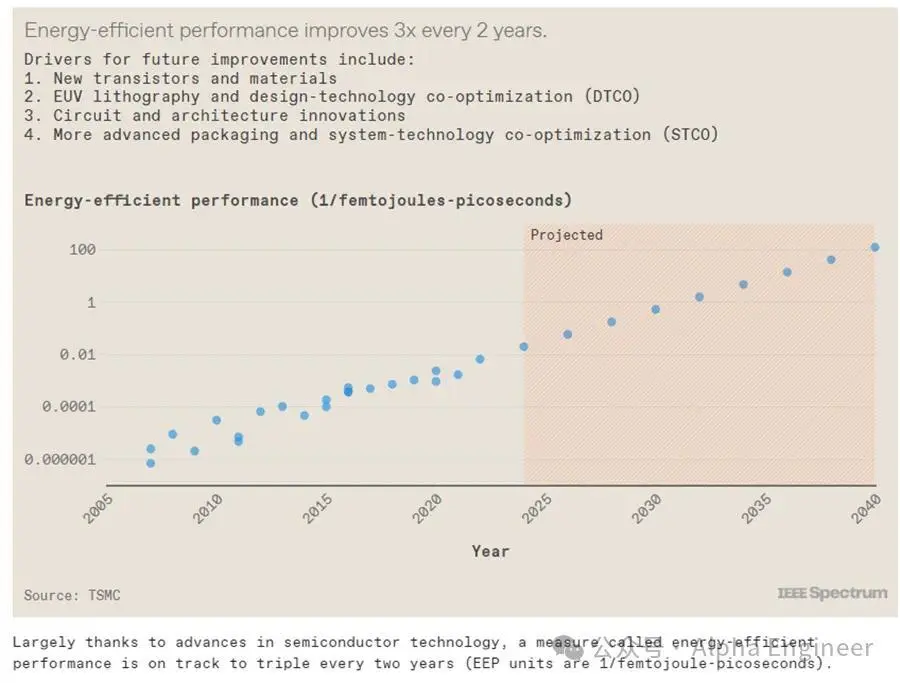

为了有效评估半导体技术创新对系统性能带来的影响,业内有一个指标叫做EEP。

EEP的全称是Energy-Efficient Performance,即能效性能,是能效与性能的综合衡量标准。

过去15年来,半导体行业的EEP呈现出每2年提高3倍的趋势。我们相信这个趋势会继续保持下去,其背后得益于新材料的应用、先进封装工艺、EUV光刻技术的发展、电路及系统架构设计的优化等等。

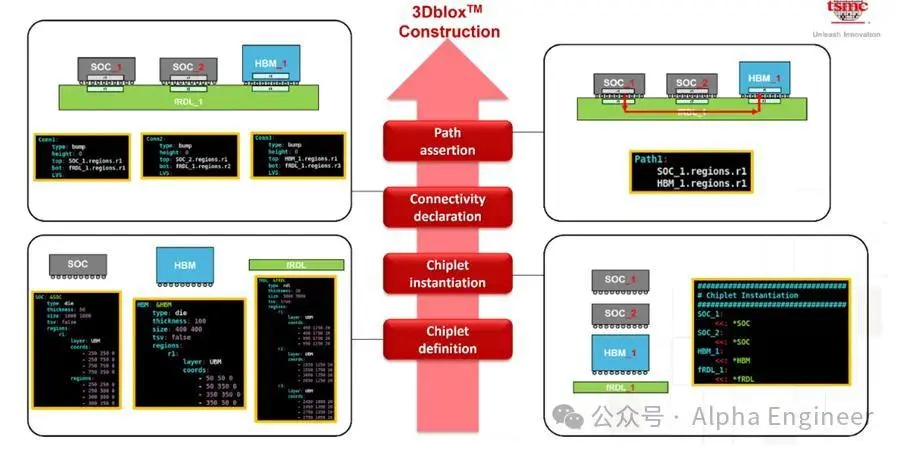

(8)3D集成电路将迎来Mead-Conway时刻

1978年,加州理工大学教授Carver Mead以及Xero PARC研究中心的Lynn Conway发明了一种通过计算机辅助设计集成电路的方法。

它们通过一组设计规则,让工程师能够轻松设计超大规模的集成电路,而无需了解太多的工艺细节。

当下3D芯片设计领域也需要同样的能力。现在一位3D芯片设计师需要了解的知识非常多,包括系统架构设计、软硬件优化、3D封装技术等等。

正如我们在1978年所做的一样,我们再次需要一种通用语言,用计算机能够理解的方式来描述3D芯片设计技术,让设计人员可以在无需考虑底层技术的同时,自由地设计3D芯片。

类似的技术正在陆续诞生,比如一项名为3Dblox的开源标准正在被越来越多的半导体技术公司和EDA公司所采用。

(9)隧道已至终点,面向无限可能的未来

过去50年,半导体技术的发展就像是走进了一条隧道,有着明确的目标和清晰的路径。所有人的目标只有一个:shrink the transistor。

现在,我们已经走到了隧道尽头。从现在开始,半导体技术的发展正式进入深水区,在隧道之外有着各式各样的可能性,等待人们去探索。